胡振國Jenn-Gwo Hwu

國立臺灣大學電子工程學研究所教授

國立臺灣大學電機工程學系教授

學歷

- 國立臺灣大學電機工程學研究所博士 ( 1985 )

- 國立臺灣大學電機工程學研究所碩士 ( 1979 )

- 國立交通大學電子工程系學士 ( 1977 )

經歷

- 國立臺灣大學電子工程學研究所教授( 合聘 ) ( 2001/8 ~迄今 )

- 國立臺灣大學電機工程學系教授 ( 1989/8 ~ 迄今 )

- 國科會工程處微電子學門召集人 ( 2005/12 ~ 2008/12 )

鑽研矽基超薄氧化層技術 挖掘耦合效應機制特徵

個人研究矽基超薄氧化層技術多年,在超薄氧化層金氧半穿隧二極體 ( MIS TD ) 耦合效應機制與元件應用探索,發現有多項特徵為前所未見,重要指標已達世界紀錄,因元件結構與現今CMOS 製程相容,具前瞻性與應用性,以專利申請與論文發表展現半導體元件創新研究能量。

研究發現對中央MIS ( p ) 固定偏壓VD,因穿隧大缺少數載子進而使電流趨飽和,外環MIS ( p ) 給予負VG,少數載子能量提升但數量減少,經耦合使中央MIS ( p ) 電流減少呈現電晶體特徵。給予PVS ( positive voltage stress ),氧化層達局部薄化,元件電流呈現提早飽和,稱為OLT ( oxide local thinning ),使得中央MIS ( p ) 可工作於小偏壓而電流提升。經Drain OLT 後,ON 電流提升,再經 Gate OLT,可使SSmin 有效減少至小9.7 mV/dec,為矽基元件紀錄。

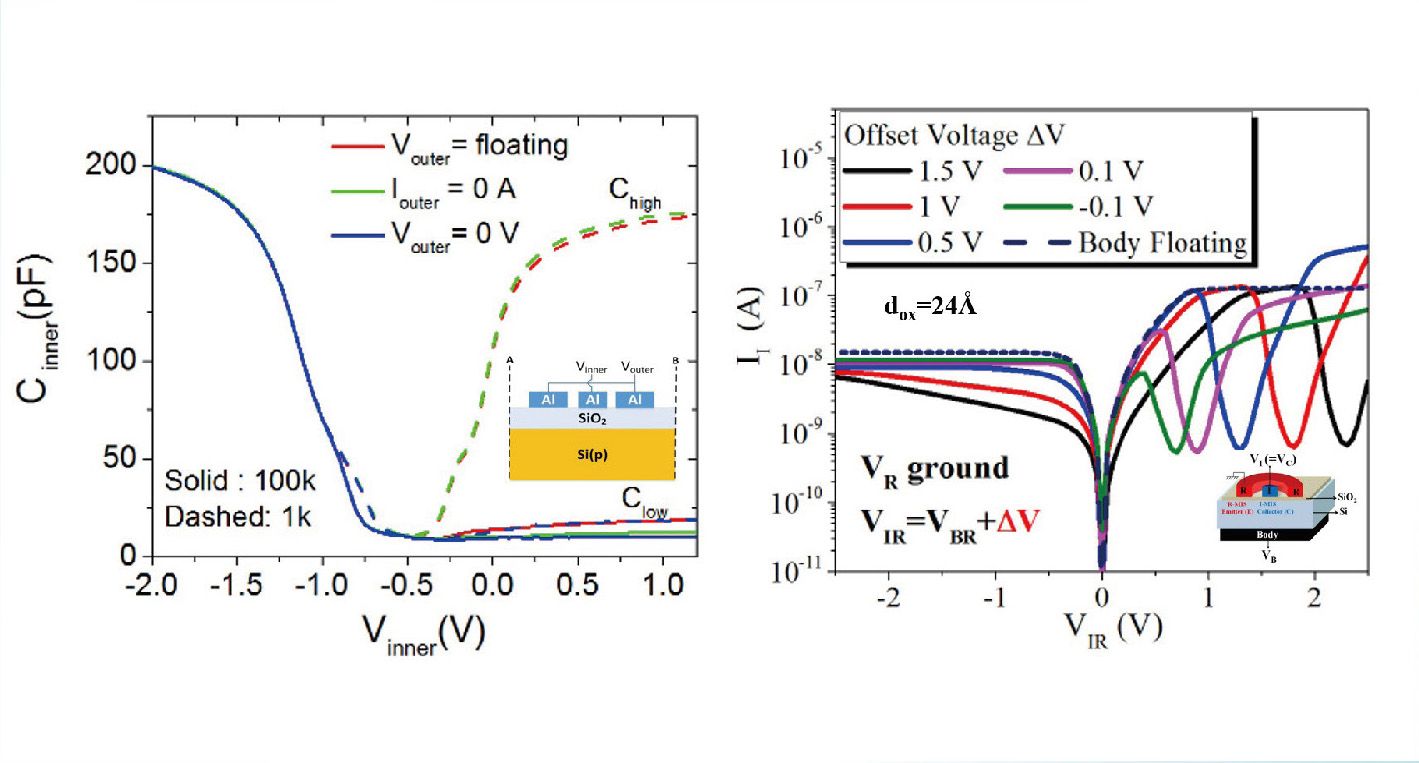

另一發現為中央MIS ( p ) 電容值於反轉區受外環MIS ( p ) 閘極之電位影響甚鉅,於閘極開路時 ( Iouter = 0 A ) 反轉電容值大,於閘極短路時 ( Vouter = 0 V ),電容值降低,因中央MIS ( p ) 於反轉區之偏壓固定,故少數載子數量固定,電容值差異明顯受外環Vouter 影響,為前所未見。因閘電極操作於 0 A 與0 V 時均屬無額外功率消耗,電路整合容易,電容雙態可做記憶體應用。給 Iouter = 0 A 得到 Chigh,切換至Vouter = 0 V 得到Clow,可重複多次操作雙態電容穩定。

此外,在耦合結構中基板偏壓改變,內外電極間之耦合條件會隨之改變,使得負轉導特徵為可調整,對於電路設計相當有用,為前所未見。經由適當的offset voltage △ V ( = VIB ) 選取,當內外電極間電壓VIR 變化時,負轉導會受△ V 影響,呈現不同之負轉導出現區,相當靈敏。所得到之最大 Peak to Valley Current Ratio ( PVCR ) 達103 以上,為矽基元件紀錄。

得獎感言

我很感謝臺大提供的優質研究環境、研究生們持續的努力與配合、加上國家給予充分的研究計畫經費,使得整個研究可以在合宜氛圍下腦力激盪,對於所觀察到的實際元件量測現象進行深入的探索分析,提出合理解釋及可能的應用。

值得一提的是,在科技部產學大聯盟制度下,與業界台積電有更進一步的研究交流,可將智財予以適當保護在先,順利發表於後,研究成果可提供給世人參考,研究生可以獲得實質研究訓練及發表論文的學習,這是學術界相當有意義的工作,也是本次可以獲得肯定的最主要原因,我再次感謝科技部與台積電持續的支持與投入。

個人勵志銘

尋找合宜的題目做喜歡的研究,持續深入探索,日以繼夜必有所成,到某地步將會發現驚奇,也就會開花結果。